Adicionador Serial Binário em Lógica Digital

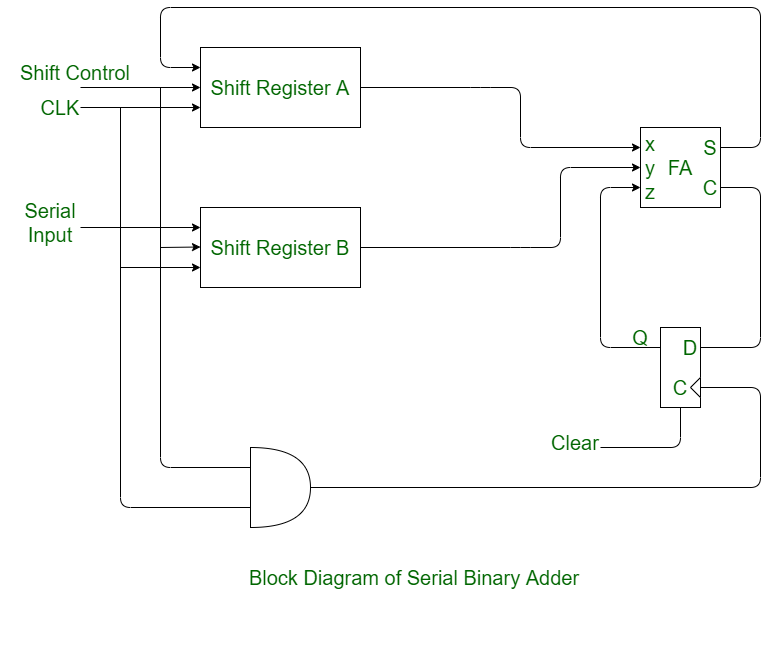

Adicionador binário serial é um circuito lógico combinacional que realiza a adição de dois números binários na forma serial. O somador binário serial realiza adição bit a bit. Dois registradores de deslocamento são usados para armazenar os números binários que devem ser adicionados.

Um único somador completo é usado para adicionar um par de bits por vez junto com o transporte. A saída de transporte a partir do adicionador total é aplicado a um flip-flop D . Depois disso, a saída é usada como transporte para os próximos bits significativos. O bit de soma da saída do somador completo pode ser transferido para um terceiro registrador de deslocamento.

Diagrama de blocos do somador binário serial:

Shift Registers :

Shift Register é um grupo de flip-flops usado para armazenar vários bits de dados. Existem dois registradores de deslocamento usados no somador binário serial. Em um registrador de deslocamento, o augend é armazenado e, em outro, o suplemento do registrador de deslocamento é armazenado.

Full Adder : Full Adder

é o circuito combinacional que pega três entradas e dá duas saídas como soma e transporte. O circuito adiciona um par de cada vez com a ajuda dele.

Flip-flop D :

a saída do carry do somador completo é aplicada no flip-flop D. Além disso, a saída do flip-flop D é usada como entrada de transporte para o próximo par de bits significativos.

Processo de Trabalho: A

seguir está o procedimento de adição usando somador binário serial:

- Etapa 1:

Os dois registradores de deslocamento A e B são usados para armazenar os números a serem adicionados. - Etapa 2:

Um único somador completo é usado para adicionar um par de bits por vez junto com o transporte. - Etapa 3:

O conteúdo dos registradores de deslocamento muda da esquerda para a direita e sua saída começando em aeb são alimentados em um único somador completo junto com a saída do flip-flop de transporte na aplicação de cada pulso de clock. - Etapa 4:

A saída da soma do somador completo é alimentada para o bit mais significativo do registro da soma. - Etapa 5:

O conteúdo do registro de soma também é deslocado para a direita quando o pulso de clock é aplicado. - Etapa 6:

Após aplicar quatro pulsos de clock, o conteúdo de dois registros (A e B) da adição é armazenado no registro de soma.

Aprenda todos os conceitos do GATE CS com aulas gratuitas ao vivo em nosso canal do youtube.

As postagens do blog Acervo Lima te ajudaram? Nos ajude a manter o blog no ar!

Faça uma doação para manter o blog funcionando.

70% das doações são no valor de R$ 5,00...

Diógenes Lima da Silva